http://dx.doi.org/10.6113/TKPE.2014.19.6.488

# 3레벨 4레그 PWM 컨버터의 커먼 모드 전압 저감

지승준<sup>1</sup>, 고상기<sup>2</sup>, 김현식<sup>1</sup>, 설승기<sup>†</sup>

# Common-mode Voltage Reduction of Three Level Four Leg PWM Converter

Seung-Jun Chee<sup>1</sup>, Sanggi Ko<sup>2</sup>, Hyeon-Sik Kim<sup>1</sup>, and Seung-Ki Sul<sup>†</sup>

#### Abstract

This paper presents a carrier-based pulse-width modulation(PWM) method for reducing the common-mode voltage of a three-level four-leg converter. The idea of the proposed PWM method is intuitive and easy to be implemented in digital signal processor-based converter control systems. On the basis of the analysis of space-vector PWM(SVPWM) and sinusoidal PWM(SPWM) switching patterns, the fourth leg pole voltage of the three-phase converter called "f leg pole voltage" is manipulated to reduce the common-mode voltage. To synthesize f leg pole voltage for the suppression of the common-mode voltage, positive and negative pole voltage references of f leg are calculated. An offset voltage is also deduced to prevent the distortion of a, b, and c phase voltages. The feasibility of the proposed PWM method is verified by simulation and experimental results. The common-mode voltage of the proposed PWM method in peak-to-peak value is 33% in comparison with that of the conventional SVPWM method. The transition number of the common-mode voltage is also reduced to 25%.

**Key words:** Pulse width modulation(PWM), Sinusoidal PWM(SPWM), Space-vector PWM(SVPWM), Digital signal processor(DSP), Common-mode voltage(CMV), Common-mode current(CMC)

#### 1. 서 론

에너지 및 환경 문제로 분산 전원 시스템에 대한 관심이 점점 증가하고 있고, 다양한 전압/주파수를 가지는 분산 전원을 전력 계통 (grid)에 연결하기 위해서는 PWM 컨버터 (converter) 시스템이 주로 사용된다. 보통의 3상 전원 시스템과의 연계를 위해서 2레벨 (level) 3레그 (leg) 토폴로지 (topology)가 간단한 구조와 제어의특성으로 널리 적용 되어 왔다. 그러나 2레벨 토폴로지에 비해 작은 필터의 적용 가능성 및 높은 운전 효율특성 때문에 멀티 레벨 토폴로지가 주목을 받고 있다.이중에 특히 Neutral Point Clamped (NPC) 및 T-type과 같은 3레벨 토폴로지가 상대적인 제어의 용이성과기술적인 성숙에 의해 점점 널리 사용되고 있다.

Paper number: TKPE-2014-19-6-2

Print ISSN: 1229-2214 Online ISSN: 2288-6281

컨버터가 계통과 연결된 상황에서는 컨버터와 계통 사이에 연결된 3개의 단상 부하들이 평형 혹은 불평형 인지에 상관없이 단상 부하에 평형 전압이 인가되게 된다. 그러나 계통 사고 등의 이유로 컨버터와 단상 부하들이 계통과 분리되고, 컨버터 단독으로 부하에 에너지를 공급하는 자립 운전 (stand-alone operation) 상황에서는 부하의 조건에 따라 단상 부하들에 걸리는 전압이 달라진다. 부하가 평형이면, 부하에 걸리는 전 압도 평형이지만, 부하가 불평형이면 3개의 단상 부하 에 걸리는 전압이 각각 달라진다. 이러한 불평형 전압 을 막기 위해서 부하와 컨버터 사이에 변압기를 이용 하여 계통이 끊어져도 변압기의 중성점을 불평형 삼상 부하의 중성점에 연결해 줌으로써 각 단상 부하의 전 압을 평형된 전압으로 유지시켜 줄 수 있다. 그러나 변압기 적용 시 효율의 감소를 가져오고 가격, 무게, 부피의 상승을 유발한다. 불평형 3상 부하에 평형 3상 전압을 공급하기 위한 또 다른 방법으로 4레그 토폴로 지(topology)가 있다. 이러한 토폴로지는 반도체의 가 격 대비 성능의 증가로 변압기를 적용하는 것에 비해 비용, 효율, 크기 면에서 장점을 가질 수 있다. 여기서 추가적인 레그는 계통의 중성점과 단상 부하들의 중성 점에 연결 된다<sup>[2]</sup>.

<sup>†</sup> Corresponding author: sulsk@plaza.snu.ac.kr, Dept. of Electrical and Computer Eng., Seoul National University

Tel: +82-2-880-7251 Fax: +82-2-878-1452

<sup>&</sup>lt;sup>1</sup> Dept. of Electrical and Computer Eng., Seoul National Univ. <sup>2</sup> Central Research Institute, Samsung Heavy Industries Manuscript received Jul. 28, 2014; accepted Sep. 4, 2014 — 논문은 2014년 전력전자학술대회 우수추천논문임

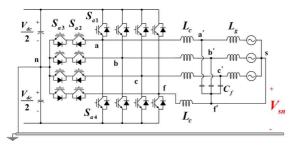

Fig. 1. System configuration.

Fig. 2. Switching patterns (a) SVPWM, (b) SPWM.

PWM 컨버터에서는 스위칭 동작을 하므로 커먼 모드 전압 (Common Mode Voltage, CMV) 이 필연적으로 존재하게 된다. 높은 주파수의 CMV는 기생 캐패시터를 통하여 커먼 모드 전류 (Common Mode

Current, CMC)를 발생시키고, 이러한 CMC는 EMI (Electro Magnetic Interference)의 근원이 된다. 이는 컨버터의 제어 시스템 자체의 오동작을 일으킬 뿐만 아니라 주위 전자 장치의 오동작을 일으키게 되는 요 인이다<sup>[3]</sup>. 이와 같은 CMC를 줄이기 위해 통상 사용하는 방법에는 두 가지가 있는데, 하나는 커먼 모드 필터 등의 수동 소자를 이용하는 것이고<sup>[4]</sup>, 다른 하나는 PWM 스위칭 패턴을 바꾸는 방법이다<sup>[5-10]</sup>. 최근의 대부분 CMV 저감 연구는 부가적인 하드웨어가 필요 없다는 장점 때문에 PWM 스위칭 패턴을 바꾸는 기법이 주를 이룬다.

이 논문에서는 그림 1과 같은 3레벨 4레그 토폴로지에서 CMV를 저감하기 위한 삼각파 비교 전압 변조방법을 제안하였다. 또한 컨버터 출력 전압의 고조파성분 억제를 위한 옵셋 전압을 유도하였다. 또한 시뮬레이션 및 실험을 통하여 제안한 PWM 방법의 유효성을 검증하였다.

# 2. 3레벨 4레그에서 기존 PWM 방법의 CMV

4레그 PWM 컨버터의 CMV는 식 (1)과 같이 표시된 다<sup>[10]</sup>

$$V_{an} + V_{bn} + V_{cn} + V_{fn} \ . \eqno(1)$$

식 (1)의 CMV는 4레그의 스위칭 상태  $(S_a, S_b, S_c, S_f)$  를 이용하여 다음 식과 같이 다시 표시할 수 있다.

$$V_{sn} = \frac{S_a + S_b + S_c + S_f}{4} \frac{V_{dc}}{2} = S \frac{V_{dc}}{8}. \tag{2}$$

여기서 스위칭 상태  $(S_x)$ 와 CMV 상태  $(S_{CMV})$ 는 아래와 같이 정의 된다.

$$S_x = \begin{bmatrix} 1 \ , (S_{x1}:on) \\ 0 \ , (S_{x2,3}:on) \\ \lfloor -1 \ , (S_{x4}:on) \end{bmatrix}, \ S_{CMV} = S_a + S_b + S_c + S_f. \quad (3)$$

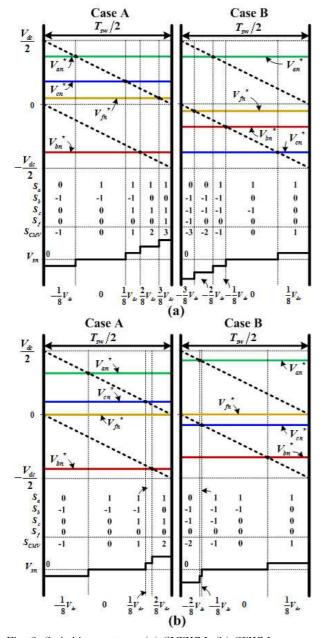

삼각파 반송파 (carrier wave) 비교 SVPWM 방법이 4레그 시스템에 적용되면 $^{[11]}$ ,  $S_{CMV}$  는 그림 2. (a)에서 보는 바와 같이 7가지(-3, -2, -1, 0, 1, 2, 3) 값을 가진다. 해당하는 CMV는  $-3/8V_{de}$ ,  $-2/8V_{de}$ ,  $-1/8V_{de}$ , 0,  $1/8V_{de}$ ,  $2/8V_{de}$ ,  $3/8V_{de}$  가 된다. 그림 2. (b)와 같이 SPWM 방법이 적용되면 $^{[12]}$ , CMV는  $-2/8V_{de}$ ,  $-1/8V_{de}$ , 0,  $1/8V_{de}$ ,  $2/8V_{de}$  가 된다.

그림 2에서  $S_{CMV}$ 가 어떤 값을 가지는지를 기준으로 모든 극전압(pole voltage) 지령은 Case A 혹은 B의 경

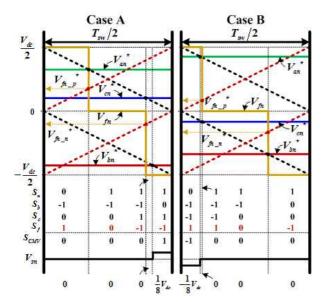

Fig. 3. Switching patterns of proposed PWM method.

우만 존재를 하고, 두 경우는 a, b, c 3개의 극전압 지령 중 양의 값을 가지는 지령의 개수로 구분되어 진다. Case A는 2개가 양이고, Case B에서는 1개가 양이 된다.

## 3. CMV 저감을 위한 PWM 방법

SPWM이 적용되면( 0),  $S_{MV}$ 에 관련한 두 가지 규칙을 확인할 수 있다. 하나는  $T_{sw}$ 동안에 삼각파 파형이 정점일 때,  $S_{CMV}$ 는 -1 (Case A) 또는 -2 (Case B)의 값을 가진다. 다른 하나는 a, b, c 극전압 지령과 삼각파 파형의 교점에서  $S_{CMV}$ 는 1씩 증가한다는 것이다.

위와 같은 규칙에 근거하여  $S_f$ 를 적절하게 만들어주면,  $S_{CMV}$ 를 최대한 0에 가깝도록 만들어 줄 수 있다. 그림 3 의 Case A에서 는 1,0,-1,-1을 가지면 되고, 이때 최종적인  $S_{CMV}$ 는 0,0,0,1이 된다. Case B인 경우에는,  $S_f$ 는 1,1,0,-1을 가지면 되고, 이때 최종적인  $S_{CMV}$ 는 -1,0,0,0이 된다. 따라서 CMV는  $0,0,0,1/8\,V_{dc}$  혹은  $-1/8\,V_{dc},0,0,0$  이 된다. 제안된 PWM 방법에서 CMV의 첨두치는  $1/4\,V_{dc}$ 가 되고,  $T_{sw}/2\,$ 동안 CMV는 1번 변경된다. 이와 같은 PWM 방법을 적용하면, SVPWM 방법에 비해 전압 사용률이 떨어지고, 스위칭 고조파 성분이 증가한다는 단점이 있으나, SVPW의 첨두치 및 변동 횟수를 줄일 수 있게 된다.

### 4. 제안된 PWM 방법의 구현

제안된 PWM 방법과 같은  $S_f$ 를 만들어주기 위해서는 f 레그 극전압이 스위칭 주기의 반 시간  $(T_{sw}/2)$  동안 2 번 변경되어야 한다. 이를 구현하기 위해서는 f 레그에

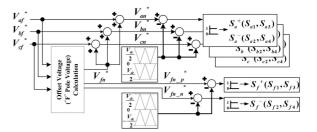

Fig. 4. Block diagram of proposed PWM method.

사용된 삼각파의 위상이 a, b, c 레그에 사용된 캐리어 파형의 위상과 180도 차이가 나야 한다. 또한 삼각파와 비교를 위한 2가지 f 레그 극전압 지령  $(V_{fn-p}^*, V_{fn-n}^*)$ 이 필요하다. 이 전압 지령들은 각각 위, 아래 삼각파의 지령으로 사용된다. 그림 3의 Case A에서  $V_{fn-p}^*$ ,  $V_{fn-n}^*$ 는 각각  $V_{dd}/2-V_{an}^*$ ,  $-V_{cn}^*$ 가 되고, Case B에서  $-V_{cn}^*$ ,  $-V_{dd}/2-V_{bn}^*$ 가 된다.

이것을 다시 일반적으로 표현하면 Case A에서  $V_{fn-p}^*$ ,  $V_{fn-n}^*$ 은 식 (4)와 같다.

$$V_{fn-p}^{*} = V_{dc}/2 - V_{\text{max }_{ole}}^{p}$$

$$V_{fn-n}^{*} = -V_{mid}^{p} .$$

(4)

여기서

$$\max_{d} = \max(V_{an}^{p}, V_{bn}^{p}, V_{cn}^{p}),$$

$$\begin{cases} V_{min_{pde}}^{p} = mid(V_{an}^{p}, V_{bn}^{p}, V_{cn}^{p}) \\ V_{min_{pde}}^{p} = \min(V_{an}^{p}, V_{bn}^{p}, V_{cn}^{p}) \end{cases}$$

$$V_{xn}^{p} = \frac{V_{xn}^{*}}{V_{xn}^{*} + V_{dd}/2, (V_{xn}^{*} < 0)}.$$

(5)

Case B에서의  $V_{fn-p}^*$ ,  $V_{fn-n}^*$ 은 식 (6)과 같다.

$$V_{fn-p}^{*} = V_{dc}/2 - V_{mid_{pole}}^{p}$$

$$V_{fn-n}^{*} = -V_{\min_{pole}}^{p}.$$

(6)

Case A에서는 식 (4), Case B에서는 식 (6)과 같이 2가지 f상 극전압 지령을 이용하면 CMV를  $\pm 1/8\,V_{dc}$ 이 내로 줄일 수 있다.

그러나  $T_{sw}/2$  동안 f 상 평균 전압은 식 (7)과 같이 0이 아니다. 따라서 3상 상 출력 전압은 불가피하게 고조파 성분을 포함하게 되고, 그 결과 각 상에 고조파 전류가 흐르게 된다.

$$V_{fn-average} = V_{fn-p}^* + V_{fn-n}^*. (7)$$

극전압 지령이 Case A에 해당하는 경우에 식 (7)은 식 (8)과 같이 다시 쓸 수 있다.

$$V_{fn-average} = (V_{dc}/2 - V_{\max_{pole}}^p) + (-V_{mid_{pole}}^p). \tag{8}$$

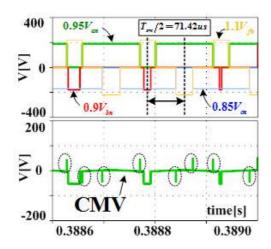

Fig. 5. Simulation results – pole voltages (  $_n, V_{bn}, V_{cn}, V_{fn}$ ) and CMV of proposed PWM method.

만약 상전압에 적절한 옵셋(offset) 전압 ( $V_{fn}^*$ )을 더할 수 있다면 식 (8)의  $V_{fn-average}$ 는 옵셋 전압과 같아야 하므로 식 (8)은 식 (9)와 같이 다시 쓸 수 있다.

$$V_{fn}^* = V_{dc}/2 - (V_{\text{max}}^p + V_{fn}^*) - (V_{mid_{above}}^p + V_{fn}^*).$$

(9)

여기서

$$\max_{hose} = \max(V_{af}^{p}, V_{bf}^{p}, V_{cf}^{p}), \\ \begin{cases} V_{mid_{plose}}^{p} = mid(V_{af}^{p}, V_{bf}^{p}, V_{cf}^{p}) \\ V_{min_{plose}}^{p} = \min(V_{af}^{p}, V_{bf}^{p}, V_{cf}^{p}) \end{cases} \\ V_{xf}^{p} = \frac{V_{xf}^{*}}{V_{xf}^{*} + V_{dc}/2, (V_{xf}^{*} < 0)}.$$

$$(10)$$

식 (9)에서 옵셋 전압을 계산하면 식 (11)과 같다.

$$V_{fn}^{*} = 1/3 \left( V_{dc}/2 - V_{\max_{phase}}^{p} - V_{mid_{phase}}^{p} \right). \tag{11}$$

같은 방식으로 Case B의 경우에 옵셋 전압을 계산하면 식 (12)와 같다.

$$V_{fn}^{*} = 1/3 \left( V_{dc}/2 - V_{mid_{phase}}^{p} - V_{\min_{phase}}^{p} \right). \tag{12}$$

Case A에서는 식 (11), Case B에서는 식 (12)와 같이 계산한 옵셋 전압을 그림 4에서의  $V_{fn}^*$ 에 대입해주면 상 전압의 왜곡을 막아줄 수 있다.

### 5. 시뮬레이션

그림 1과 같은 형태의 5 kW T-type 3레벨 4레그 컨 버터를 대상으로 시뮬레이션을 수행하였다. 스위칭 주파 수는 7 kHz이고, 데드 타임 (dead time) 은 2 us로 설정

Fig. 6. Simulation results - CMVs of SVPWM, SPWM and proposed PWM method.

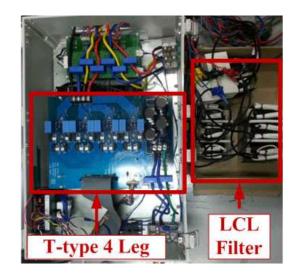

Fig. 7. Experimental setup.

하였다. 그리고 직류단 전압은 400 V, 계통 선간 전압은 220 Vms로 상정하였다.

그림 5는 제안된 PWM 방법이 적용되었을 때의 극전압들과 해당하는 CMV 파형으로, 극전압들은 그림 3에서 Case B에 해당한다. f 레그의 극전압이 제안된 PWM 방법대로 다른 3개의 극전압에 맞추어 값이 변경되는 것을 볼 수 있다. 따라서 예상한 바와 같이 CMV가 50V ( $\pm 1/8V_{dc}$ ) 이내로 유지되는 것을 확인할 수있다. 여기서 CMV는 그림 1에서 직류단 전압의 중성점(n)과 계통의 중성점(s)에 걸리는 전압을 측정한 것이다.

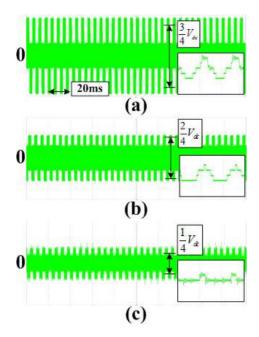

Fig. 8. CMVs (a) SVPWM, (b) SPWM (c) proposed PWM.

그러나 데드 타임의 영향으로 점선 원안의 파형과 같이 짧은 펄스 형태의 CMV가 나타나기도 한다.

그림 6에서는 SVPWM, SPWM, 제안된 PWM 방법에서의 CMV를 표시해 주었다. 각각의 CMV 첨두치는  $/4~_c,2/4V_{dc},1/4V_{dc}$ 인 것을 알 수 있고, 확대된 파형에서  $T_{sw}/2$ 동안 CMV의 변화 횟수는 4,~3,~1인 것을 알수 있다.

### 6. 실 험

시뮬레이션과 같은 시스템 구조, 조건에서 실험을 수행하였다. 실제 실험에 사용한 시스템은 그림 7과 같이 구현 되었다. 그림 8은 PWM 컨버터가 계통과 연계되어 정격 전류 제어를 하면서 각각의 PWM을 사용하였을 때, CMV 전압이 어떻게 나타나는지를 보여주고 있다. 시뮬레이션과 마찬가지로 CMV는 직류단 전압의 중성점(n)과 계통의 중성점(s) 사이의 전압을 측정한 것이다. SVPWM, SPWM, 제안된 PWM 방법의 CMV 첨두치는 각각  $3/4V_{dc}(=300V)$ ,  $2/4V_{dc}(=200V)$ ,  $1/4V_{dc}(=100V)$ 가된다. 3가지 PWM 방법 중에 제안된 PWM 방법에서의 CMV가 가장 작은 것을 알 수 있다. 또한 각각의 확대된 CMV 파형에서 변화 횟수가 각각 4, 3, 1이 되는 것을 알 수 있다.

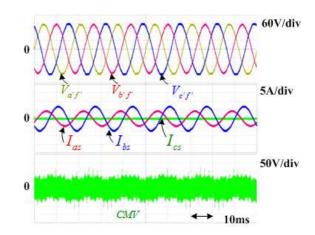

그림 9는 제안된 PWM 방법에서 옵셋 전압( $V_{fn}^*$ )의 영향을 보기 위한 파형이다. 그림 9. (a)는 옵셋 전압이 적절하게 보상되지 않았을 경우( $V_{fn}^*=0$ )의 파형으로, f 레그의 극전압은 3고조파 성분을 가지게 되는데 a, b, c 레그 극전압에 f 레그 극전압이 미리 보상되지 않아 상전류에 3고조파에 해당하는 왜곡이 생기게 된다. 그러나

Fig. 9. Phase currents and CMV of proposed PWM (a) when  $V_{fn}^* = 0$ , (b) when  $V_{fn}^*$  is properly compensated using equation (11), (12).

Fig. 10. Capacitor voltages, phase currents and CMV of proposed PWM.

옵셋 전압을 수식 (11), (12)와 같이 적절하게 계산하여 적용하면 a, b, c 레그의 극전압이 f 레그의 극전압을 보 상하므로 그림 9. (b) 와 같이 상전류의 왜곡이 없어진 것을 볼 수 있다.

계통과 PWM 컨버터의 연결이 끊어진 자립 운전 (stand-alone operation) 시 제안된 PWM 방법이 제대로 동작하는지 확인하기 위해 불평형 단상 부하 조건에서 실험을 수행하였다. 사용된 전압 제어 방법은 개루프 제어 방식으로 과도 상태 안정도 증가 및 부하 전류에 의한 전압 강하 보상의 특징이 있다<sup>[13]</sup>. 그림 10에서의 전류에서 볼 수 있듯이 부하가 불평형 되어 있어도 각 단상 부하에 평형 전압이 인가되는 것을 볼 수 있다. 또한그때의 CMV는 50V ( $\pm 1/8V_{dc}$ ) 이내로 억제되고 있는 것을 볼 수 있다.

# 7. 결 론

본 논문에서는 3레벨 4레그 시스템의 CMV 저감을 위한 삼각파 비교 전압 변조 기법을 제시하였고, CMV를 최대한 0에 가깝게 만들어 주었다. 이를 위한 추가된 레그의 지령 전압들을 유도하였다. 또한 상전압 왜곡을 막기 위한 옵셋 전압을 계산하였다. 제안된 PWM 기법의 검증을 위하여 시뮬레이션과 실험을 수행하였다. 시뮬레이션 및 실험 결과를 통하여, 제안된 PWM 방법을 적용하면 CMV의 크기와 변화 횟수가 SVPWM에 비하여 66% ( /4  $_c \rightarrow 1/4 V_{dc}$ ), 75% ( $4 \rightarrow 1$ ) 만큼 감소함을 확인하였다.

#### References

- [1] M. Schweizer, I. Lizama, T. Friedli, and J. W. Kolar, "Comparison of the chip area usage of 2-level and 3-level voltage source converter topologies," in *IECON* 2010 36th Annual Conference on IEEE Industrial Electronics Society, pp. 391-396, 2010.

- [2] R. Zhang, V. H. Prasad, D. Boroyevich, and F. C. Lee, "Three-dimensional space vector modulation for four-leg voltage-source converters," *Power Electronics*, *IEEE Transactions on*, Vol. 17, pp. 314–326, 2002.

- [3] G. L. Skibinski, R. J. Kerkman, and D. Schlegel, "EMI emissions of modern PWM AC drives," *Industry Applications Magazine*, *IEEE*, Vol. 5, pp. 47–80, 1999.

- [4] S. Ogasawara and H. Akagi, "Modeling and damping of high-frequency leakage currents in PWM inverter-fed AC motor drive systems," *Industry Applications, IEEE Transactions on*, Vol. 32, pp. 1105–1114, 1996.

- [5] E. Un and A. M. Hava, "A near-state PWM method with reduced switching losses and reduced common-mode voltage for three-phase voltage source inverters," *Industry Applications, IEEE Transactions on,* Vol. 45, pp. 782-793, 2009.

- [6] C. C. Hou, C. C. Shih, P. T. Cheng, and A. M. Hava, "Common-mode voltage reduction pulsewidth modulation techniques for three-phase grid-connected converters," *Power Electronics, IEEE Transactions on*, Vol. 28, pp. 1971-1979, 2013.

- [7] M. Cacciato, A. Consoli, G. Scarcella, and A. Testa, "Reduction of common-mode currents in PWM inverter motor drives," *Industry Applications*, *IEEE Transactions on*, Vol. 35, pp. 469-476, 1999.

- [8] L. Yen-Shin and S. Fu-San, "Optimal common-mode voltage reduction PWM technique for inverter control with consideration of the dead-time effects-part I: basic development," *Industry Applications*, *IEEE Transactions on*, Vol. 40, pp. 1605–1612, 2004.

- [9] A. M. Hava, x, and E. n, "A high-performance PWM algorithm for common-mode voltage reduction in three-phase voltage source inverters," *Power*

- Electronics, IEEE Transactions on, Vol. 26, pp. 1998–2008, 2011.

- [10] L. Zeng, L. Jinjun, and L. Jin, "Modeling, analysis, and mitigation of load neutral point voltage for three-phase four-leg inverter," *Industrial Electronics*, *IEEE Transactions on*, Vol. 60, pp. 2010–2021, 2013.

- [11] K. Jang-Hwan and S. Seung-Ki, "A carrier-based PWM method for three-phase four-leg voltage source converters," *Power Electronics, IEEE Transactions on*, Vol. 19, pp. 66-75, 2004.

- [12] C. Dae-Woong, K. Joohn-Sheok, and S. Seung-Ki, "Unified voltage modulation technique for real-time three-phase power conversion," *Industry Applications, IEEE Transactions on,* Vol. 34, pp. 374-380, 1998.

- [13] S. J. Lee, H. S. Kim, and Seung-Ki Sul, "A novel control method for the compensation voltages in dynamic voltage restorers," in *Applied Power Electronics Conference and Exposition*, 2004. APEC '04. Nineteenth Annual IEEE, Vol. 1, pp. 614-620, 2004.

# 지승준(池丞焌)

1980년 8월 15일생. 2003년 서울대 공대 전기공학부 졸업. 2005년 동 대학원 전기·컴퓨터 공학부 졸업(석사). 2005년~2011년 삼성전자 생산기술연구소 책임연구원. 2011년~현재 동 대학원 전기·컴퓨터 공학부 박사과정.

### 고상기(高尙起)

1989년 7월 5일생. 2012년 서울대 공대 전기공학부 졸업. 2014년 동 대학원 전기·컴퓨터공학부 졸업(석사). 2014년~현재 삼성중공업 연구원.

#### 김 현식(金炫植)

1988년 10월 18일생. 2013년 서울대 공대 전기·정보공학부 졸업. 2013년~현재 동 대 학원 전기·컴퓨터공학부 석박사과정.

#### 설승기(薛承基)

1958년 3월 25일생. 1980년 서울대 공대 전기공학과 졸업. 1983년 동 대학원 전기공학과 졸업(석사). 1986년 동 대학원 전기공학과 졸업(공박). 1986년~1988년 University of Wisconsin, Madison 연구원. 1988년~1990년

LG산전 책임연구원. 2003년~2004년 일본 Yaskawa Electric Corp. 상임연구고문. 1991년~현재 서울대 전기·정보공학부 교수. 2005년~2007년 서울대 공대 부학장. 2008년~2011년 기초 전력연구원 원장. 2011년 ICPE'11 General Chairman. 당 학회 JPE Editor-in-Chief.