# 매트릭스 컨버터의 출력 전류 리플 저감을 위한 PWM 방법

김 성 민, 설 숭 기 서울대학교 전기컴퓨터 공학부

## PWM method of Matrix converter for reducing output current ripple

Sungmin Kim, Seung-Ki Sul

School of Electrical Engineering & Computer Science, Seoul National University, Seoul, Korea.

## **ABSTRACT**

메트릭스 컨버터(Matrix Converter:MC)는 기본적으로 9개의 양방향 스위치를 이용한 전력변환장치이다. 입력 전압의 크기에 따라 일정 범위 내의 전압을 합성할 수 있으며, 다이오드 정류기를 이용하는 인버터에 비해 입력전류를 정현파로 만들수 있는 장점을 가지고 있다. 다수의 스위치를 이용하여 출력전압을 합성하기 때문에 제어가 복잡하다는 단점이 있으나, 반대로 여러 가지 방법으로 전압을 합성할 수 있는 가능성과 회로 구성의 확장 가능성이 크다는 장점도 있다. 본 논문에서는 입력 전압의 순시적인 선간전압을 이용한 새로운 공간 벡터 변조(Space Vector Modulation: SVM)방법을 제안하고, 기존 SVM과 동일한 구현 가능성 및 새로운 유사 멀티레벨(Multi-level) SVM으로의 확장성을 보인다. 유사 멀티레벨 SVM을 사용하였을 경우 출력 전류의 리플이 감소하고 고조파특성이 개선됨을 Matlab 시뮬레이션을 통해 검증한다.

#### 1. 서 론

매트릭스 컨버터는 9개의 양방향 스위치를 이용하여 3상 교류 입력 전압을 직류 변환 과정을 거치지 않고 바로 원하는 주 파수와 크기를 갖는 교류 전압을 출력하는 전력변환장치이다. 매트릭스 컨버터는 1980년 Venturini와 Alesina의 연구[1] 이후로 많은 제어방법이 제안되어 왔다. 전압형 인버터의 제어 방법인 SVPWM 방법이 매트릭스 컨버터의 제어 방법으로 확장적용되었으며.[2] 최근에는 Carrier Based Modulation을 통해 SVM과 동일하게 PWM을 구현하는 연구도 발표되었다.[3]

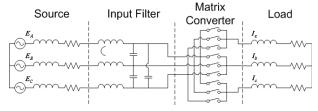

매트릭스 컨버터는 2종류의 형태로 구분될 수 있다. 9개의 양방향 스위치로 입력과 출력을 직접 연결하는 direct matrix converter(MC) 구조와, 입력단을 정류하는 부분과 출력단으로 전압을 합성하는 부분이 연결되어 있는 indirect MC 구조로 나뉜다.<sup>[4]</sup> 일반적으로 매트릭스 컨버터는 direct MC를 의미하며, 그 구성은 그림1과 같다.

그림 1. Matrix Converter system의 구성

Fig 1. System configuration of matrix converter

제안된 방법에서는 매트릭스 컨버터를 순시적으로 3개의 가상 DC link가 존재하는 인버터로 가정하여 SVM 방법을 통해 스위칭 상태(Switching State)를 일반적으로 결정할 수 있다. 제안된 방법을 통하여 기존 SVM을 구현할 수 있으며, 출력 전압 지령에 따라 가장 근접한 전압 벡터를 활용하여 합성하는 유사 멀티레벨 SVM을 구현할 수 있다.

#### 2. 본 론

### 2.1 매트릭스 컨버터의 접근 관점

매트릭스 컨버터는 입력 교류 전압을 출력 교류 전압으로 변환하는 장치이다. 전압형 인버터가 DC link 전압을 PWM하여 필요한 전압을 합성하는 것처럼 매트릭스 컨버터는 순시적으로 입력전압의 선간전압을 PWM하여 출력 전압 지령을 합성하게 된다. 결과적으로 매트릭스 컨버터는 순시적으로 3개의 크기가 다른 가상의 DC link(그림 2)를 활용할 수 있는 전압형 인버터라고 생각할 수 있다.

그림 2. 매트릭스 컨버터의 가상 DC link Fig 2. Virtual DC link of matrix converter

#### 2.2 출력 전압과 입력 전류 합성 방법

매트릭스 컨버터는 출력 전압 합성과 입력 전압의 정현파 합성을 동시에 만족하는 제어 방법을 필요로 한다. 매트릭스 컨버터를 부하에서 바라보면 전압을 만들어주는 전압원 (voltage source)이고, 입력에서 보면 합성된 전압에 의해 전류가 만들어지는 전류원(current source)으로 간주할 수 있다. 본 논문에서는 출력 전압을 합성하기 위해서 가상 DC link 평면 (그림2)에 SVM방법을 적용하는 것을 제안한다.

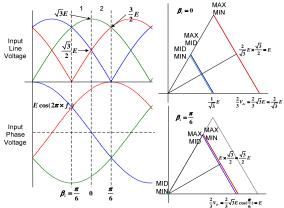

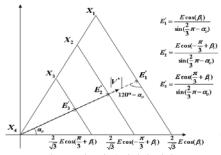

그림3은 입력 상전압에 따른 순시적인 가상 DC link를 나타 낸 것이다. 위 전압 평면에서 출력 전압 지령에 따라 가장 가 까운 전압을 이용하여 전압을 합성하게 된다. 따라서 특정 전

E: 입력 상전압의 Peak value

MAX : 입력 상전압이 가장 큰 상(phase) MID : 입력 상전압이 두 번째 큰 상(phase) MIN : 입력 상전압이 가장 작은 상(phase) β; : 입력 상전압의 위상(0~π/6으로 치환) 그림 3. 입력 상전압에 따른 가상 DC link

Fig 3. Virtual DC link depend on input phase voltage

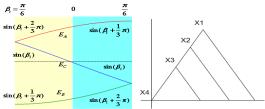

압 지령에 대해 순시적으로 존재하는 3개의 입력 선간 전압과 영벡터가 어떻게 사용되는지를 일반적으로 계산해야 한다. 각 가상 DC link가 전압 합성에 사용되는 통류율(Duty Factor)을 차례로 X1, X2, X3, X4라고 정의하면, 그림4와 같이 입력 전압 의 상전압과 통류율 관계를 표현할 수 있다. 이때 입력 전류의 역률을 1로 제어하기 위해서는 순시적으로 입력단 각 상에 출 력단이 연결되는 시간이 식(1)-(3)과 같아야한다.

$$E_A: X1 + X3 = \sin(\beta_i + \frac{2}{3}\pi) \times T$$

(1)

$$E_B: X1 + X2 = \sin(\beta_i + \frac{1}{3}\pi) \times T$$

(2)

$$E_C: X2 - X3 = \sin(\beta_i) \times T \tag{3}$$

그림 4. 입력 상전압의 크기 및 순시적인 선간전압의 통류율 Fig 4. Input phase voltage and instantaneous duty factor of input line voltage

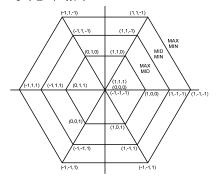

그램5는 전압 평면 위에서 순시적인 가상 DC link와 출력 전압 지령을 극좌표계로 표현한 것이다.( $|V^*| \angle \alpha_o$ ) 가상 DC link의 유효 백터 시간을 이용하여 출력 전압을 합성하면 식(4)와 같이 표현할 수 있다. 식(4)를 통해 전압전달률(Transfer ratio, q)는 식(5)와 같이 구할 수 있다.

$$\begin{split} |V^*| &= E_1^{'} X 1 + E_2^{'} X 2 + E_3^{'} X 3 \\ &= \frac{E}{\sin((2\pi/3) - \alpha_o)} (\cos(\beta_i) X 1 \\ &+ \cos(-\frac{1}{3}\pi + \beta_i) X 2 + \cos(\frac{\pi}{3} + \beta_i) X 3) \\ q &= \frac{|V^*|}{E} = \frac{1}{\sin((2\pi/3) - \alpha_o)} (\cos(\beta_i) X 1 \\ &+ \cos(-\frac{1}{3}\pi + \beta_i) X 2 + \cos(\frac{\pi}{3} + \beta_i) X 3) \end{split} \tag{5}$$

그림 5. 전압 평면에서 순시적인 가상 DC link Fig 5. Space vector and virtual DC link

입력 전류 합성의 기준이 되는 식(1)-(3)을 출력 전압 합성 식에서 얻어지는 식(5)에 대입하면 식(1)-(3)에서 사용되는 상 수 T는 식(6)과 같다. 식(6)을 식(1)-(3)에 대입하여 가상 DC link의 유효 통류율는 식(7)-(10)과 같은 관계식을 갖는다.

$$T = \frac{2}{\sqrt{3}} \sin(\frac{2}{3}\pi - \alpha_o)q \tag{6}$$

$$X1 = -X3 + \frac{2}{\sqrt{3}}qsin(\frac{2}{3}\pi - \alpha_o)sin(\beta_i + \frac{2}{3}\pi) \tag{7}$$

$$X2 = X3 + \frac{2}{\sqrt{3}}qsin(\frac{2}{3}\pi - \alpha_o)sin(\beta_i)$$

(8)

$$X1 + X2 + X3 + X4 = 1 (9)$$

$$0 \le X1, X2, X3, X4 \le 1 \tag{10}$$

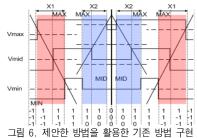

각 가상 DC link의 유효 시간 관계식에는 1개의 자유도가 존재한다. X3(순시적으로 가장 작은 입력 선간 전압)을 0으로 하면 2개의 큰 가상 DC link를 사용하게 되므로 기존 SVPWM방법(그림6)과 동일하게 구현할 수 있다.<sup>[4]</sup>

Fig 6. Conventional Switching pattern using proposed method

기존 방법은 출력 전압 지령과 관계없이 항상 가장 큰 가상 DC link와 두 번째로 큰 DC link를 활용하게 된다. 그러나 제안된 방법은 필요에 따라 순시적으로 4종류의 전압을 선택적으로 사용할 수 있다.

## 2.3 유사 멀티레벨 전압 합성 PWM

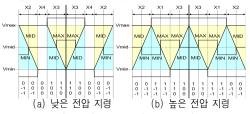

제안된 방법은 그림7과 같이 출력 전압 지령의 크기에 따라 가까운 유효 전압 백터를 활용할 수 있기 때문에 멀티레벨 전압 합성과 유사한 결과를 얻을 수 있다.

그림 7. 출력 전압 크기에 따른 유사 멀티레벨 전압 합성 SVM Fig 7. Quasi-Multilevel SVM along with voltage reference

## 2.4 시뮬레이션

R-L 부하에 대해 Matlab을 이용하여 시뮬레이션하였다. 시 뮬레이션 파라메터는 표1과 같다.

표 1 시뮬레이션 파라메터

Table 1 Simulation parameters

| R 부하(3Φ) | <b>R=5</b> Ω | L 부하(3Φ)  | L=1mH   |

|----------|--------------|-----------|---------|

| 입력선간전압   | 220[V]       | 입력주파수     | 60[Hz]  |

| 입력필터 L   | 100[mH]      | 입력필터 C(Δ) | 35[μF]  |

| 입력필터 R   | 0.1[Ω]       | 스위칭주파수    | 10[kHz] |

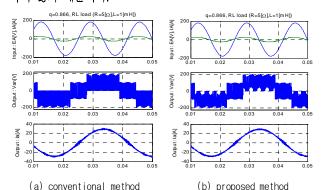

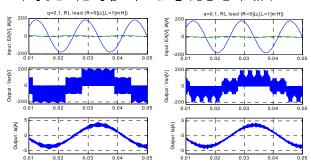

#### 2.4.1 높은 출력 전압 지령에 대한 전압 합성

그림 8은 전압 전달률 0.866에서 기존 SVPWM과 제안된 방법 각각의 입력 및 출력 전압, 전류의 시뮬레이션 결과이다. 제안된 방법의 결과 중에서 출력 상전압의 PWM 결과를 보면, 부분적으로 멀티레벨 전압 합성이 일어났음을 확인할 수 있다. 높은 전압을 합성할 경우, 가장 큰 입력 선간 전압과 두 번째로 큰 입력 선간 전압을 유효 벡터로 사용하고 영벡터를 사용하지 않기 때문이다.

그림 8. q=0.866에서 입력전압/전류, 출력상전압, 출력전류

Fig 8. Input Voltage/Current, Output phase voltage, Output phase current at q=0.866

## 2.4.2 낮은 출력 전압 지령에 대한 전압 합성

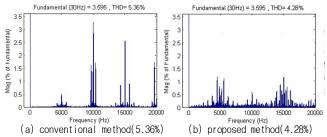

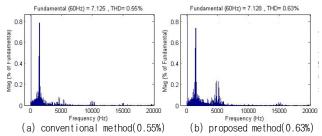

그림 9는 전압 전달률 0.1에서 기존 SVM과 제안된 방법의 입력 및 출력 전압, 전류의 시뮬레이션 결과이다. 제안된 방법의 결과를 보면, 출력 전압이 높을 때와는 달리 가장 큰 입력 선간 전압을 사용하지 않고 영벡터를 사용하여 출력 전류의 고조파 특성을 개선할 수 있다. 그림 10은 출력 전류의 주파수 분석 결과이다. 전류 리플이 감소하였을 뿐만 아니라 고조파 성분을 여러 주파수 대역으로 흩어지게 하는 효과를 얻을 수 있다. 그림11은 입력 전류의 주파수 분석 결과이다. 입력 전류의 고조파 성능은 기존 방법보다 조금 떨어짐을 볼 수 있다.

그림 9. q=0.1에서 입력전압/전류, 출력상전압, 출력전류 Fig 9. Input Voltage/Current, Output phase voltage, Output phase current at q=0.1

그림 10. q=0.1에서 출력 전류의 주파수 분석 결과

Fig 10. FFT of output current at q=0.1

그림 11. q=0.1에서 입력 전류의 주파수 분석 결과

Fig 11. FFT of input current at q=0.1

#### 3. 결 론

제안된 SVM방법은 스위칭 참조표를 사용하지 않으면서 순시적으로 존재하는 가상 DC link를 활용하여 다양한 PWM 패턴을 구현할 수 있다. 기존 SVM 방법과 동일한 스위칭 패턴을 구현할 수 있으며, 특히 순시적으로 3개의 가상 DC link를 활용하기 때문에 출력 전압 지령에 가장 근접한 유효 벡터를 활용함으로써 유사 멀티레벨 전압 합성이 가능하다.

제안된 방법으로 기존 SVM방법의 스위칭 패턴을 동일하게 구현할 수 있음을 보였으며, Matlab simulation을 통해 제안된 방법으로 가상 DC link를 활용한 유사 멀티레벨 전압 합성과 그로 인해 출력 상전압의 모양과 출력 전류의 FFT를 비교 분석함으로 타당성을 증명하였다.

## 참 고 문 헌

- [1] Patrick W. Wheeler, Jose Rodriguez, Alejandro Weinstein, "Matrix Converter: A Technology Review", in IEEE Trans. Ind. Elect. Vol. 49, No. 2, pp. 276-288, April 2002.

- [2] Domenico Casadei, Giovanni Serra, Angelo Tani, Luca Zarri, "Matrix Converter Modulation Strategies: A New General Approach Based on Space-Vector Representation of the Switch State", in IEEE Trans, Ind Elect, Vol. 49, No. 2, pp. 370-381, April 2002.

- [3] Young-Doo Yoon, Seung-ki Sul, "Carrier-Based Modulation Technique for Matrix Converter", in IEEE Trans, Power Elect, Vol. 21, No. 6, November 2006.

- [4] Johann W. Kolar, Frank Schafmeister, Hans Ertl, "Novel Three-Phase AC-AC Sparse Matrix Converter", in IEEE Trans. Power Elect, Vol. 22, No. 5, pp. 1649-1661, September 2007.